# Keysight M9330A Arbitrary Waveform Generator 15-bit, 1.25 GS/s

### Introduction

The Keysight Technologies M9330A arbitrary waveform generator (AWG) is capable of creating high-resolution waveforms for radar, satellite, and frequency agile communication systems. Each channel of the M9330A operates at 1.25 GS/s and features 15 bits of vertical resolution giving designers the most realistic, wideband waveforms available from a commercial AWG.

- 1.25 GS/s and 15 bits of vertical resolution per channel provides exceptionally realistic wideband waveforms

- Dual output channels drive both single-ended and balanced designs without the need for baluns or hybrids

- Extended waveform memory and advanced sequencing engine offers long scenario simulations

- Multiple module synchronization provides multi-emitter simulations

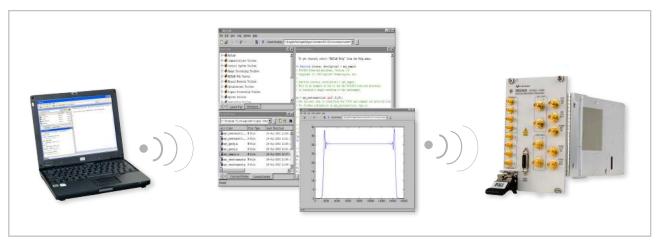

- Multiple programmatic interfaces enable easy integration into existing test environments

#### Generate wide bandwidth and wide dynamic range signals, simultaneously

The M9330A is a 4-slot 3U PXI module that offers dual differential output channels to drive both single-ended and balanced designs. The AWG also supports advanced sequencing and triggering modes to create event-based signal simulations. Multiple M9330A modules can be synchronized for the generation of phase-coherent, multi-emitter scenarios. Waveform development tasks are simplified using the AWG's numerous programmatic interfaces including complete instrument control from the MATLAB command line and from LabView. When the M9330A is combined with a wideband I/Q upconverter, modulation bandwidths of 1 GHz can be realized at microwave frequencies for authentic signal simulations for IF and RF subsystem test.<sup>1</sup>

#### Unprecedented

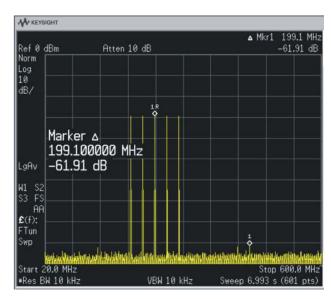

The M9330A gives designers access to the most advanced Digital-to-Analog (DAC) technology available in a commercial AWG. Each module incorporates two high-speed DACs to create 500 MHz of signal bandwidth and ≤ −65 dBc spurious free dynamic range (SFDR) across each channel. Users have the choice of driving their designs differentially from the DAC outputs or single-ended through multiple signal-conditioning paths. Although some AWGs require users to make a trade-off between the number of output channels and differential outputs, the M9330A provides both − allowing you to drive your designs and eliminating the need for baluns or hybrids in the test path. In addition, each channel can output waveforms as an IF or as a baseband signal for I/Q upconversion.

Figure 1. Generate wideband waveforms with unprecedented signal fidelity.

Keysight E8267D PSG signal generator with Option 016, wideband I/O inputs or Keysight N8212A performance vector upconverter with Option 016; either option could be used.

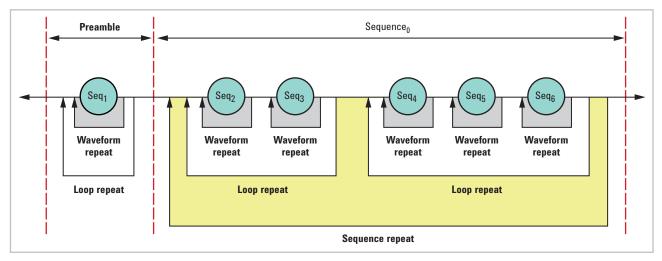

Figure 2. Create sophisticated signal scenarios by looping and nesting waveforms.

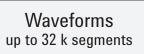

### Create long scenario simulations

Multiply the effective size of on-board memory through the use of the M9330A's advanced sequencing engine. Uniquely define how waveform segments are played through looping and nesting of stored waveforms.

This capability also gives users the ability to create new signals from existing waveforms by playing only subsegments of waveform memory. For users developing a large number of waveform scenarios the PXI backplane substantially reduces waveform download times compared to traditional LAN and GPIB. The M9330A's complete waveform and sequencer memories can be typically reloaded in less than 1 second.

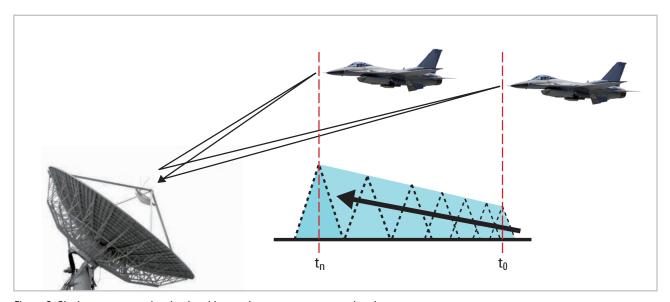

Figure 3. Closing targets can be simulated by ranging parameters on each pulse.

### System scalability

Create phase-coherent, multi-emitter simulations using the M9330A's precision SYNC clock. A single M9330A can drive a total of eight AWG modules to synchronize their outputs on a sample-by-sample basis. Any number of modules can be synchronized with simple driver hardware. The AWG also includes multiple front-panel triggers and markers for complete system synchronization.

Figure 4. Four M9330A modules fit conveniently inside an 18 slot PXI chassis.

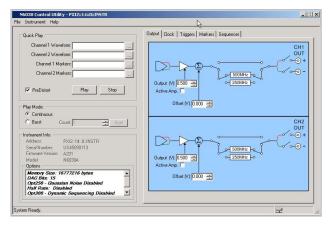

#### Ease-of-use

The M9330A's graphical user interface guides developers through module setup and waveform file transfers. Users can quickly configure the instrument's signal conditioning paths, marker and trigger lines, sample and reference clock sources, and simple sequencing functions. More sophisticated sequencing functions are available through the instrument's numerous programmatic interfaces. The M9330A supports interfaces for MATLAB, LabView, IVI-C, IVI-COM, and VEE frameworks.

Figure 5. Directly import and play waveforms from the Quick Play menu.

Figure 6. Play waveforms files directly from the MATLAB command line.

### ENHANCED CAPABILITIES FOR THE M9330A SERIES!

### Dynamic Sequencing (Option 300)

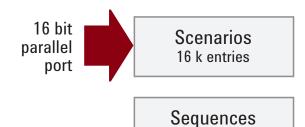

The dynamic sequencing software enables radar and military communications engineers to build custom signal scenarios on the fly. Engineers can dynamically access up to 16 k of previously stored sequences through a 16-bit interface and replay these complex waveforms to respond to changing threat environments, or to create signals where the next waveform to be played is not known in advance.

### Dynamic Synthesis (Option 330)

The direct digital synthesis (DDS) software enables radar and emerging communications engineers to create basic waveforms in the AWG's memory and then modify their behavior with profiles for amplitude modulation, phase modulation, and frequency modulation. This enables engineers to simulate testing without the time and expense of field trials, such as in-flight and in-orbit testing. This option can also be used to simulate fading profiles in receiver testing for satellite and 4 G signals, such as multiple input and multiple output formats (MIMO).

32 k entries

Figure 7. Create signals where next waveform to be played is not known in advance.

Figure 8. Define signals by carrier frequency and modulation - instant by instant.

### KEY CHARACTERISTICS

| Channels                                                     |                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Two independent channels available as baseband or IF outputs | CH1: Single-ended and differential CH2: Single-ended and differential                                                                                                                                                                                        |

| Modulation bandwidth                                         | 500 MHz per channel (1 GHz IQ bandwidth)                                                                                                                                                                                                                     |

| Resolution                                                   | 15 bits (1/32,768 levels)                                                                                                                                                                                                                                    |

| Output spectral purity – (CH1 and CH2)                       | <ul> <li>Harmonic distortion:</li> <li>≤ -65 dBc for each channel DC to 500 MHz</li> <li>Non-harmonic spurious:</li> <li>≤ -75 dBc for each channel 1 kHz to 500 MHz</li> <li>Noise floor:</li> <li>&lt; -150 dBc/Hz across the channel handwidth</li> </ul> |

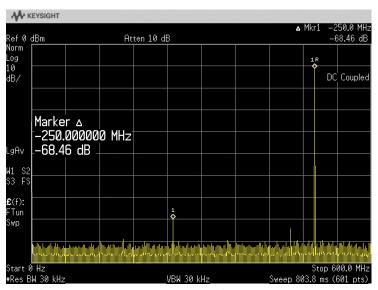

Figure 9. Excellent harmonic and spurious performance are available across the full bandwidth of each channel.

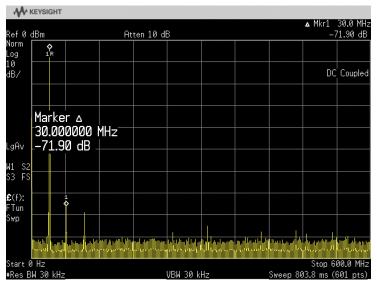

Figure 10. Spurious performance outstanding at low signal frequencies.

### KEY CHARACTERISTICS CONTINUED

| Sample clock                     |                                                                                        |

|----------------------------------|----------------------------------------------------------------------------------------|

| Internal                         | Fixed 1.25 GS/s                                                                        |

| Internal clock output            | +3 dBm nominal                                                                         |

| External clock input             | Tunable 100 MS/s to 1.25 GS/s                                                          |

| External clock input drive level | +5 to –15 dBm typical                                                                  |

| Phase noise characteristics      | 1 kHz: –95 dBc/Hz<br>10 kHz: –115 dBc/Hz<br>100 kHz: –138 dBc/Hz<br>1 MHz: –150 dBc/Hz |

| Noise floor                      | –150 dBc/Hz                                                                            |

| Accuracy                         | Same as 10 MHz timebase input                                                          |

| Frequency reference     |                                                 |

|-------------------------|-------------------------------------------------|

| Input drive level       | +2 to +12 dBm into 50 $\Omega$ (+2 dBm nominal) |

| Waveform length         | 8 MS per channel (16 MS with option 016)        |

| Minimum waveform length | 128 samples                                     |

| Waveform granularity    | 8 samples                                       |

#### Segment

1 to 32 k unique segments can be defined consisting of waveform start and stop address, repetitions, and marker enable flags.

#### **Segment loops**

A total of 1 million (220) loops can be defined for each segment. Loops can be configured to advance in one of three modes:

- The segment loop plays once and waits at the end of the loop for a trigger.

- Segment loop is repeated continuously until a trigger is received.

- Automatically advances to the next segment after completing the specified number of loop repetitions.

#### Repeat

The waveform loop repeats until the number of wave form loop repetitions is met.

#### Sequences

Up to 32 k total unique waveform sequences can be defined. A sequence is a contiguous series of waveform segments.

#### Advanced sequencing

Enables users to build and playback scenarios, which are comprised of one or more sequences.

#### **Scenarios**

1 to 16 k pointers can be assigned to play pre-defined sequences. Sequence play begins with the first sequence entry and continues uninterrupted until the last entry is played. The table repeats until stopped.

## KEY CHARACTERISTICS CONTINUED

#### Scenario jump modes

Scenario jumps determine how a sequence responds to a jump trigger. There are no discontinuities in a scenario jump other than those imposed by the waveform data. Three modes are available to control scenario

#### Jump immediate

- Jumps immediately to the next specifie scenario address with a fixed latency.

#### End of waveform

- The current waveform (including repeats) is completed before jumping to a new scenario.

#### End of scenario

- The current scenario is completed before jumping to a new scenario. Jump latency is the longer of either the jump immediate latency or the length of the remaining scenario.

| Dynamic Sequencing (Option 300) |                                                                                                                                                                                 |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input                           | 20-pin mini-D connector                                                                                                                                                         |

| Input levels                    | All pins configured as 2.5 volt LVCMOS inputs. A logic low must fall within the $-0.2$ to $+0.5$ volt window. A logic high must be within the window of $+2.0$ to $+2.8$ volts. |

| Number of address bits          | 13 bits per channel                                                                                                                                                             |

| Total number of addressable     | Scenarios 16 k                                                                                                                                                                  |

| Data rate for dynamic data      | 100 ns                                                                                                                                                                          |

| Data latency                    | Same as front panel trigger inputs. Software pointers may also be used to point to pre-defined scenarios over the PCI backplane though latencies are not deterministic.         |

| Direct Digital Synthesis (Option 330) |                                                           |

|---------------------------------------|-----------------------------------------------------------|

| Output frequency resolution           | 1 Hz                                                      |

| Frequency modulation                  | Deviation from 0 to 125 MHz (250 MHz peak-peak)           |

| Phase modulation                      | Deviation from -180 to +180 degrees in 0.022 degree steps |

| Amplitude modulation                  | Modulation depth from 0 to 100% with 15-bit resolution    |

| Single channel bandwidth              | 400 MHz (800 MHz I/Q)                                     |

| External triggers         |                                                                                                                    |

|---------------------------|--------------------------------------------------------------------------------------------------------------------|

| Number of inputs          | 8 each (4 SMB female frontpanel connectors plus four software triggers over the PCI backplane from host processor) |

| Trigger polarity          | Negative/positive                                                                                                  |

| Trigger impedance         | 2k Ω                                                                                                               |

| Maximum input level       | ±4.5 volts                                                                                                         |

| Input sensitivity         | 250 mV                                                                                                             |

| Trigger threshold         | -4.3 volts to +4.3 volts                                                                                           |

| Trigger timing resolution | Clock/8 (6.4 ns at full rate)                                                                                      |

| Trigger latency           | 34* clock/8 (217.6 ns at full rate)                                                                                |

| Trigger uncertainty       | < 50 ps                                                                                                            |

| Minimum trigger width     | 12.8 ns at full clock rate                                                                                         |

| Trigger delay             | Programmable from 1 to 256 sync clock cycles with 1 sync clock cycle resolution <sup>1</sup>                       |

## KEY CHARACTERISTICS CONTINUED

| External markers  Markers can be defined for each waveform comment                                                              |                                                                                                                                                |           |  |

|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|

| Markers can be defined for each waveform segment.                                                                               | 4 each SMB female                                                                                                                              |           |  |

| Number of outputs                                                                                                               |                                                                                                                                                |           |  |

| Marker polarity                                                                                                                 | Negative, positive                                                                                                                             |           |  |

| Output impedance                                                                                                                | 50 Ω                                                                                                                                           |           |  |

| Marker low level                                                                                                                | 100 mV nominal into high impedance load                                                                                                        |           |  |

| Marker high level                                                                                                               | 3.2 volts nominal into high impedance load                                                                                                     |           |  |

| Marker timing resolution                                                                                                        | Clock/8 (6.4 ns at full rate)                                                                                                                  |           |  |

| Marker latency                                                                                                                  | Marker precedes analog output and is adjustable in 2 sample of period steps.                                                                   | clock     |  |

| Marker latency repeatability                                                                                                    | < 100 ps                                                                                                                                       |           |  |

| Marker width                                                                                                                    | Programmable with from 1 to 256 sync clock cycles <sup>1</sup>                                                                                 |           |  |

| Marker delay                                                                                                                    | Programmable from –8 to 502 sample clock cycles, with 2 sam cycle resolution                                                                   | iple cloc |  |

| Module synchronization                                                                                                          |                                                                                                                                                |           |  |

| Supports system scaling for any number of M9330A modules. A s repeatability. Driver boards may be used to scale any number of n | single module can support fan-out of 8 M9330A modules for precise triggering modules.                                                          | g and     |  |

| Sync clock output level                                                                                                         | 800 mV p-p (50 Ω, AC coupled)                                                                                                                  |           |  |

| Sync clock input sensitivity                                                                                                    | 100 mV p-p minimum into 50 $\Omega$ AC coupled                                                                                                 |           |  |

| Analog output                                                                                                                   |                                                                                                                                                |           |  |

| Output connector                                                                                                                | SMA female                                                                                                                                     |           |  |

| Output impedance                                                                                                                | 50 Ω                                                                                                                                           |           |  |

| Analog output levels                                                                                                            | The following output levels are specified into 50 $\Omega$                                                                                     |           |  |

|                                                                                                                                 | Single-ended   Differential                                                                                                                    | fset)     |  |

|                                                                                                                                 |                                                                                                                                                | .001,     |  |

| Corrected passband flatness                                                                                                     | ±1 dB DC - 200 MHz ±2.5 dB DC - 500 MHz (with 1.25 GHz clo                                                                                     |           |  |

| Corrected passband flatness Corrected passband group delay                                                                      | ±1 dB DC - 200 MHz ±2.5 dB DC - 500 MHz (with 1.25 GHz clo<br>±500 ps DC - 200 MHz ±1 ns DC - 500 MHz (with 1.25 GHz clo                       | ck)       |  |

| · · · · · · · · · · · · · · · · · · ·                                                                                           | ,                                                                                                                                              | ck)       |  |

| Corrected passband group delay Reconstruction filters                                                                           | ±500 ps DC - 200 MHz ±1 ns DC - 500 MHz (with 1.25 GHz clo<br>500 MHz and 250 MHz realized as 7-pole Cauer Chebychev filt                      | ck)       |  |

| Corrected passband group delay                                                                                                  | ±500 ps DC - 200 MHz ±1 ns DC - 500 MHz (with 1.25 GHz clo<br>500 MHz and 250 MHz realized as 7-pole Cauer Chebychev filt                      | ck)       |  |

| Corrected passband group delay Reconstruction filters Pulse response                                                            | ±500 ps DC - 200 MHz ±1 ns DC - 500 MHz (with 1.25 GHz clor<br>500 MHz and 250 MHz realized as 7-pole Cauer Chebychev filt<br>thru-line output | ck)       |  |

## GENERAL CHARACTERISTICS

| Power       |                                                                  |  |

|-------------|------------------------------------------------------------------|--|

| Supply      | +3.3 VDC, 11.2 W<br>+5 VDC, 22 W<br>+12 VDC, 5 W<br>–12 VDC, 5 W |  |

| Total power | 43.2 W                                                           |  |

#### **Environmental**

Samples of this product have been type tested in accordance with the Keysight Environmental Test Manual and verified to be robust against the environmental stresses of Storage, Transportation, and End-use; those stresses include but are not limited to temperature, humidity, shock vibration, altitude, and power line conditions. Test methods are aligned with IEC 60068-2 and levels are similar to MIL-PRF-28800F Class 3.

| altitude, and power line conditions. Test methods are aligned with IEC 6006 | 8-2 and levels are similar to MIL-PRF-28800F Class 3.                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating temperature                                                       | 0 °C to +55 °C                                                                                                                                                                                                                                            |

| Storage temperature                                                         | −20 °C to +70 °C                                                                                                                                                                                                                                          |

| Relative humidity                                                           | Type tested: 10 to 90% at 40 °C (non-condensing)                                                                                                                                                                                                          |

| Altitude                                                                    | 0 to 2000m (6500 ft) above sea level                                                                                                                                                                                                                      |

| Safety                                                                      | Designed for compliance to IEC 61010-1:2001                                                                                                                                                                                                               |

| EMC                                                                         | Meets the conducted and radiated emissions and immunity requirements of IEC 61326:2002 when tested with EMC shielded filler panels separating the controller and the M9330A module, and in all open slots. The RFI gaskets must be oriented to the right. |

| Weight                                                                      | 1.14 kg (2.5 lb)                                                                                                                                                                                                                                          |

| Security                                                                    | All user data stored in volatile memory                                                                                                                                                                                                                   |

| Dimensions                                                                  | 3U, 4-slot PXI module<br>8.1 x 13 x 21.6 cm (3.2 x 5.1 x 8.5 inches)                                                                                                                                                                                      |

| ISO compliance                                                              | This modular instrument is manufactured in an ISO-900 registered facility in concurrence with Keysight Technologies commitment to quality.                                                                                                                |

### ORDERING INFORMATION

| Model      | Description                                               |

|------------|-----------------------------------------------------------|

| M9330A     | Arbitrary waveform generator with 8 MS memory per channel |

| Option     | Description                                               |

| M9330A-M16 | Waveform memory expansion to 16 MS memory per channel     |

| M9330A-300 | Enabling software for 16-bit dynamic sequencing           |

| M9330A-330 | Direct digital synthesis software                         |

| M9330A-350 | Function generator software                               |

Figure 11. Keysight M9330A AWG with controller in PXI chassis.

NOTE: For the M9330A to work properly, at least one PXI chassis and one PXI controller type must be available.

#### Web resources

Visit our web sites for additional product information and literature.

M9330A arbitrary waveform generator www.keysight.com/find/M9330A

Signal simulation systems

www.keysight.com/find/signalsimulation

Aerospace and defense test and measurement products and services

www.keysight.com/find/ad

Test and measurement accessories www.keysight.com/find/accessories

N8241A/N8242A arbitrary waveform generator synthetic instrument modules

www.keysight.com/find/synthetic

#### myKeysight

#### myKeysight

#### www.keysight.com/find/mykeysight

A personalized view into the information most relevant to you.

#### www.pxisa.org

PCI eXtensions for Instrumentation (PXI) modular instrumentation delivers a rugged, PC-based high-performance measurement and automation system.

#### www.keysight.com/quality

Keysight Electronic Measurement Group DEKRA Certified ISO 9001:2008 Quality Management System

#### **Keysight Channel Partners**

#### www.keysight.com/find/channelpartners

Get the best of both worlds: Keysight's measurement expertise and product breadth, combined with channel partner convenience.

www.keysight.com/find/modular

For more information on Keysight Technologies' products, applications or services, please contact your local Keysight office. The complete list is available at: www.keysight.com/find/contactus

#### **Americas**

Canada (877) 894 4414 Brazil 55 11 33 51 7010 Mexico 001 800 254 2440 United States (800) 829 4444

#### Asia Pacific

1 800 629 485 Australia China 800 810 0189 Hong Kong 800 938 693 India 1 800 112 929 Japan 0120 (421) 345 080 769 0800 Korea Malaysia 1 800 888 848 Singapore 1 800 375 8100 0800 047 866 Taiwan Other AP Countries (65) 375 8100

#### Europe & Middle East

Belgium 32 (0) 2 404 93 40 Denmark 45 45 80 12 15 358 (0) 10 855 2100 Finland 0825 010 700\* France \*0.125 €/minute Germany 49 (0) 7031 464 6333 Ireland 1890 924 204 Israel 972-3-9288-504/544 Italy 39 02 92 60 8484 Netherlands 31 (0) 20 547 2111 Spain 34 (91) 631 3300 Sweden 0200-88 22 55 United Kingdom 44 (0) 118 927 6201

For other unlisted countries: www.keysight.com/find/contactus (BP-04-23-14)

www.keysight.com